Wei Shaojun and Liu Leibo Research Team Proposed New Approach for Software/Hardware Co-design to Greatly Improve the Programmability of Reconfigurable Computing Chips

The 44th International Symposium on Computer Architecture (ISCA) was held in Toronto, Canada. On this Symposium, Li Zhaoshi, doctoral student at the Institute of Microelectronics, Tsinghua University, made the report of Aggressive Pipelining of Irregular Applications on Reconfigurable Hardware. This research finding greatly improves the programmability of reconfigurable computing chips.

Reconfigurable computing chips, which are commonly recognized as one of the important development directions for future computing chips, can be modified for their arithmetic and interconnection functionalities after tape-out (manufacturing integrated circuits using silicon materials) to implement spatial mapping from applications to arithmetic elements, and have both the high flexibility of general-purpose processor and the high efficiency of application-specific integrated circuits. However, it is commonly held, both in academia and industry, that reconfigurable computing chips have serious defects in programmability, since programming irregular applications such as graph analytics and sparse linear algebra on such chips is a daunting task for software developers. This problem, if remains unsolved, would serious hinder the wide-spreading of reconfigurable computing chips and the further progress of the software/hardware co-design methodology of reconfigurable computing chips.

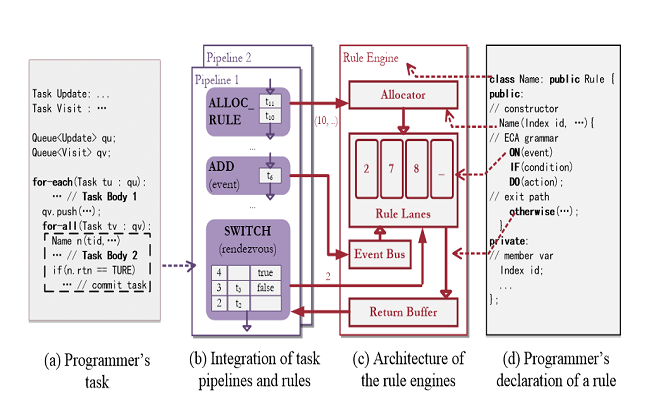

With respect to this difficult situation, Wei Shaojun and Liu Leibo research team from the Institute of Microelectronics proposed a software/hardware co-design approach oriented to the application-specific design and programming model on the basis of hardware architecture features. According to this approach, firstly, the computing pat tern of an irregular application is analyzed to create a reconfigurable programming model specific to the irregular application. In this model, one irregular application is declared as a group of tasks subject to parallel execution, with the dependency among tasks being described using rules. Using such rules, the programmer may describe the conditions under which the dependency among tasks may be established. Then, this application task will be automatically converted into hardware acceleration logic on reconfigurable computing architecture (as shown in the figure below). The task corresponds to one or more concurrent pipelines, which are synchronized by evaluating rules during runtime to implement parallel execution with the help of fine-granularity pipelining parallelism. Experiments show that, the acceleration performance obtained by using this approach is equivalent to that of the most advanced high-performance server CPUs at present, and is much better than the existing auto-generated result using high-level synthesis on reconfigurable computing architecture. This approach successfully solves the internationally recognized problem of efficient execution of irregular applications on reconfigurable computing architecture and greatly improves the programmability of reconfigurable computing chips, hence removing the obstacles for expanding the application of such chips and paving the way for the development of software/hardware co-design methodology.

Fig 1: A Reconfigurable Programming Model Proposed By Wei Shaojun and Liu Leibo Research Team

This major breakthrough in reconfigurable computing chips achieved by the Wei Shaojun and Liu Leibo research team, which is the result of the team's long-term in-depth research in the reconfigurable computing field, is also closely connected to the research cooperation project between the team and US Intel Corporation. In January 2016, Tsinghua University and Intel Corporation executed an agreement and declared to jointly engage in the development of "new general CPUs combining the reconfigurable computing technologies of Tsinghua University and the X86 architecture of Intel." Intel Corporation will offer investments to Tsinghua University in three years to achieve the objective of large-scale application of reconfigurable computing technologies in commercial fields such as cloud computing and data centers. This is Intel's first direct cooperation for the research of high-performance CPU products with a university throughout the world, and one of the largest individual investments made by the company in universities in the world. This project has achieved significant progress - the software/hardware reference design platform (as shown in the figure below) has been released in April 2017; next, the CPU engineering sample chip will be tapped out.

The ISCA is a major symposium in the computer architecture field. Many fundamental ideas in modern computing chips, such as the superscalar architecture, multi-layer cache, synchronized multithread, and cache coherence are firstly proposed in the ISCA. Of the paper presented by Li Zhaoshi on this Symposium, the corresponding author is Liu Leibo, Associate Professor; the paper is co-authored by Deng Yangdong, Associate Professor at the School of Software, Tsinghua University, and Yin Shouyi, Associate Professor at the Institute of Microelectronics, Tsinghua University.

The Wei Shaojun, Liu Leibo, and Yin Shouyi research team of the Institute of Microelectronics has engaged in long-term R&D in reconfigurable computing. From the 11st Five-Year Plan to the 13th Five-Year Plan, with the continuous support from the National Natural Science Foundation, National High-tech R&D Program (863 Program) Project, and National Science and Technology Major Project, the team has published nearly 40 papers on IEEE Transactions, nearly 30 papers on major international symposiums, and one monograph - Reconfigurable Computing, and has been granted with nearly 40 patents for invention. The key technologies have been employed in industrial applications in information security chips, programmable logic devices, and wearable computing chips.